-

Posts

2,524 -

Joined

-

Last visited

-

Days Won

149

Content Type

Profiles

Forums

Blogs

Gallery

Everything posted by latigid on

-

sneakthief, I see some issues with one standard of input: If a bipolar CV (like an LFO) is plugged in, the negative portion of the waveform will be clipped to ~0 V by the Schottky diode. Also for nominal signals of say 0-5 V you lose half the ADC resolution as the full scale input is 10 V. But the option should be there to choose your own pre-ADC treatment. I will get around to a board layout at some point, just a bit busy at the moment.

-

Wow, looks awesome! So, now we have a gate to MIDI converter -- any thoughts on CV-MIDI conversion at 1 V/octave? With the AIN scaling/protection circuits it seems to be difficult to decide on one standard, so I propose on a final panel a mixture of 0-5, 0-10 and -5 to +5 inputs, hopefully that's workable with the correct offsets. Alternatively each input could have an attenuator: http://www.falstad.com/circuit/#%24+1+4.9999999999999996E-6+47.65948060424672+58+15.0+60%0Ar+640+352+704+352+0+20000.0%0Az+912+352+912+304+1+0.805904783+3.3%0Az+912+400+912+352+1+0.805904783+3.3%0Ag+912+400+912+432+0%0AR+912+304+912+272+0+0+40.0+3.3+0.0+0.0+0.5%0AR+400+336+368+336+0+4+50.0+10.0+10.0+0.0+0.5%0Ap+912+352+960+352+1%0Aa+528+352+624+352+0+15.0+-15.0+1000000.0%0Ag+528+368+528+400+0%0Ar+528+336+480+336+0+20000.0%0Ar+464+336+400+336+0+20000.0%0Ar+496+432+496+496+0+100.0%0Ar+544+304+592+304+0+20000.0%0Ar+592+304+640+304+0+20000.0%0Aw+640+352+624+352+0%0Aw+528+336+528+304+0%0Aw+528+304+544+304+0%0Ag+400+432+400+448+0%0Aa+736+352+816+352+0+15.0+-15.0+1000000.0%0Aw+736+368+736+400+0%0Aw+736+352+736+336+0%0Ag+736+400+736+432+0%0Aw+736+352+704+352+0%0Aw+736+336+736+288+0%0Ar+736+288+832+288+0+20000.0%0Aw+816+352+816+320+0%0Aw+816+320+832+320+0%0Aw+832+320+832+288+0%0Aw+640+352+640+304+0%0Ar+816+352+912+352+0+100.0%0A174+400+368+448+432+0+10000.0+0.9455000000000001+Resistance%0Aw+480+336+464+336+0%0Aw+464+400+464+336+0%0Aw+464+400+448+400+0%0Ao+5+64+0+39+20.0+0.0015625+0+-1%0Ao+6+64+0+38+5.0+9.765625E-5+0+-1%0A'>Falstad sim, never a bad thing with modular patches.

-

You might've fried your LCD, that's easy to do. You describe shorting the backlight, well if you've applied a high current across any of the data lines that could knock out some of the circuitry. Do you have the option of using a second backlight for a test? If so, be sure you don't have any shorts that might repeat the process and outcome.

-

With the discussion on the CV V2 topic I'm thinking about what this means for the SEQ application. I would like to have both in a modular set up: MBSEQ for, well, sequences, and MBCV for interesting envelopes, LFOs, bussed knob controllers, scopes etc. There's a bit of overlap: the SEQ sends out 8 channels of CV/Gate and DIN SYNC while the MBCV can additionally output more clock signals and receive analogue inputs and a clock as control sources. The use of balanced line drivers will be useful for both boxes for AOUT, but how about the digital signals? The hardware config file for the SEQ lists SR outputs for gates, so is there a possibility of avoiding J5A/B etc. and just sending the balanced DOUT SRIO chain instead? And what about LED indication for the gates? Could a different SR output a 5 V signal to turn a gate on and off? Reading the config file maybe this is not possible, what is the explanation? The parts count would be a bit lower than using common emitter LED drivers.

-

Try here: http://www.muffwiggler.com/forum/viewtopic.php?t=102469&postdays=0&postorder=asc&start=0

-

Hmm, I had a try at putting 32 sockets on a 4.05" board (basically the max. height for a Eurorack PCB): 8 gate 8 CV 8 AIN 7 Clock 1 Sync in and it's pretty tight even at 2.2" (for a 12 HP panel), especially with another multipin connector and mounting holes. I suggest a DB-25 (or whatever connector) is mounted on a PCB with all of the interfacing circuitry (line receivers, analogue input protection circuits, pass-through for AOUT and DOUT). All of the other sockets could be panel mounted and wired to MTA 100-style connectors or similar. I know the trend is towards super shallow modules with no panel wiring but this would give a better return on investment for PCB space. Also it is customisable and more flexible for other modular formats (5U, Serge etc.) or even standalone MBCV enclosures.

-

Quick and naive question: are the serial clocks independent; could they be shared too?

-

I was considering a dual use board, one for MBseq and one for MBCV. This is for us old farts who are still on STM32F1 cores! So we could get away with a 15 pin connector for the digital serial signals and a 9 pin for AINs.

-

Great job TK! What about this for the cable pinning?: Unfortunately this leaves no room for clock signals (DIN sync/start). Shall we move to a larger cable like DC-37? http://en.wikipedia.org/wiki/D-subminiature Otherwise a higher density version might be an option, the problem then becomes finding a source for the more esoteric connectors...

-

Yep, a fair amount of work... http://processors.wiki.ti.com/index.php/CC3000_Serial_Port_Interface_(SPI)

-

Hasn't anybody thought of a touchpad so far?

latigid on replied to Ravager's topic in Design Concepts

Hey, They also sell capacitive TS overlays, just check through the menu on the left hand side. As far as I know these will also work with multi-touch gestures. As the interface is USB I guess all of the scanning hardware is compacted into the frame. Best of luck and let us know how you go! Many Greets, Andy Ah, maybe they're infrared?? -

Hasn't anybody thought of a touchpad so far?

latigid on replied to Ravager's topic in Design Concepts

I was thinking of a non-tablet solution for a MIDIbox touchpad and came across these: http://www.cyclotouch.com.au/product_info.php?products_id=2468 (you can also check out the other kits). My thought was to design a 16x16+1 LED array PCB, then overlay a transparent panel with the touch matrix interfacing to a Core module running the BLM code. In the end, a commercial tablet already has an integrated processor, WiFi and a long-life battery for wireless connectivity. -

New topic: How about skipping ethernet altogether and going directly to WiFi? Adafruit offer a cheap breakout module running over SPI: http://www.adafruit.com/products/1469 Is there a free SPI buss for this purpose? I notice the STM32F4 board does not yet have an ethernet connector.

-

Even when that signal is buffered? JBdiver reports successful signal transfer to his breakout module using only the 541 buffer of LPC17

-

Let's just think about this a bit more: 8 gates, but up to 64 with DOUT/DIO_MATRIX. DIN SYNC is 1 start/stop but up to 7 clock divisions/multiples. AOUT is really 6 signals (Vs, Vd, SO(SI), SC, RC1 and RC2) but Vs is common to the Core and doesn't need a separate ground. 1 sync input to control the master clock/ forwarded to the additional clock outs. What about analogue inputs? These would be pretty cool to interface from a modular system back to the Core. Diode clamps to protect the input pins? We're getting into quite a few signal lines now, too many for a DB-15! But for a basic usecase: 8 gates 5 AOUT 1 clock start 7 clock out 1 sync in 8 AIN 1 signal ground 31 pins ---> DB-36/Centronics? With only one clock out you'd be back to DB-25.

-

Okay, it makes sense for all the gates to be on J5A/J5B (different to the other Cores). Right, I see the MIDI IO on J11E. For MBCV V2 I guess J5A/B will be used as analogue inputs then? >>> Maybe I will create a board for STM32F1 and LPC17 and we can sort out another one later for F4. Best regards, Andy

-

TK, do you have thoughts on pinouts for the "J5C" connector on STM32F4? I will put together a DB-15 breakout/level shifter board for Gates 1-8, DIN Start and Clock, and MIDI OUT 3 (no room on the DB-15). Will it be more like STM32F1 or LPC17? Thanks, Andy

-

The back of the board is a better place to put them, although you only really need a header for J1 (/J2), the rest could be wired directly. Try sliding off the plastic base (or cutting it) and push each pin out individually. Divide and conquer is the motto for multi-pin desoldering.

-

Getting closer: Data lines are okay?

-

Okay, I will not use my version in this way as the connections will be "sammich" style to another board. But I agree, polarised connectors make good sense. Unfortunately that makes the board bigger, but I needed to give proper clearance to the mounting holes anyway. So I moved the trimmers around and that leaves room for another connector: J2 for serial output. Can I please check pins with you because the AOUT_NG does not seem to match 1:1 with the newer Cores' J19? AOUT : Vs Vd CS SI SC AOUT_LC : Vs Vd SO SC RC AOUT_NG : Vs Vd SO RC MD (?, from wiki picture) : Vs Vd FS DIN SCLK (connections to DAC on schematic) AINSER64: Vs Vd DI SC RC1 Vs Vd DO SC RC2 _____| |_____ CORE(32): Vs Vd SO SC RC1 Vs Vd SI SC RC2 _____| |_____ So, are these connections correct ? CORE(32): Vs Vd SO SC RC1 Vs Vd SI SC RC2 ______| |______ AOUT_EURO J1: Vs Vd DIN SCLK RC1 J3 chip select Vs Vd nc SCLK RC2 RC1/RC2 => FS ______| |______ AOUT_EURO J2: Vs Vd DOUT SCLK RC1 Vs Vd nc SCLK RC2 ______| |______ Sorry for the confusion, there is essentially one ground (both top and bottom layers) but GND and AGND are connected only at one point on the board. There is a "bridge" for Vd and Vref to travel on. My question was: should this bridge be on both top and bottom layers? Thanks! I'll keep chipping away at it.

-

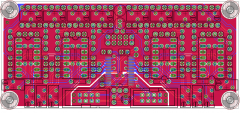

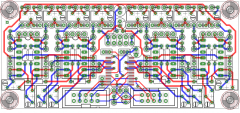

PCB layouts without and with GND plane: Routing was a bit tight for this format, but I think it works okay. I added a chip select line and put the DOUT signal on the same connector. Hopefully this is okay if somebody wants to chain more than one module. I isolated AGND and GND, and both top and bottom planes are connected. Is this a good idea? On the AOUT_NG PCB only the top layer is connected.